QXS320F280049RevA

- Parameters

- Package|Pinout|Dimensions

- Characterization

- Clarification

Main Frequency

150MHz

Kernel Architecture

Dual Core (Computing)

IEEE754 Single-Precision Floating Point Unit (FPU)

Have

Trigonometric Function Gas Pedal(TMU)

Have

Module On Complex Mathematics(VCU-I)

Have

CLA

-

CLB

-

Instruction Storage IRAM

Dual Core Sharing 256KB

Data Storage DRAM

Dual-Core Shared 256KB

Meticulously FLASH

1MB

DMA

6

System Peripherals

-

32-Bit CPU Timer

6

Window Watchdog Timer

1

GPIO

22、23

AGPIO

12、14、21

ADC resolution (bit)

12

Number ADC Number

3

SamplingG Rate

3M

Number Of Channels ADC Input / Ch.

21

CMPSS

5、6、7

DAC

12bit

12bit DAC

2

PGA

4、5、7

Programmable Gain Amplifier Amplification

3 6 12 24 48

PMBus

1

I2C

1

CAN FD (CAN2.0 Compatible)

2

SPI

2

SCI (uart compatible)

2

LIN (supports switching to uart mode)

1

FSI

1

16bit/32bit EMIF

-

USB2.0

-

EtherCat

-

EPWM Channel

24

HRPWM

16

HHRPWM

-

eCAP

7

HRCAP

2

eQEP

2

SDFM

2、4

Operating temperature range (°C)

-40℃~125℃

Package Type

LQFP64、LQFP100、VQFN 56

Package Size / mm*mm

-

Typology

General Purpose

Availability

Filling

| Type Code | Typology | Number of pins | Length*Width(mm) | Height/Maximum Height(mm) | Pitch(mm) | Spacing | Package Drawing |

|---|---|---|---|---|---|---|---|

| PZS | LQFP100 | 100 | 14X14 | 1.4/1.6MAX | 0.5 | Not Uploaded | |

| PMS | LQFP64 | 64 | 10X10 | 1.4/1.6MAX | 0.5 | Not Uploaded | |

| RSHS | VQFN56 | 56 | 7X7 | 0.75-0.9/1MAX | 0.4 | Not Uploaded |

The QXS320F280049RevA is a 32-bit processor benchmarked against TI's TMS320F28004x family. It is mainly targeted at real-time control applications (e.g., industrial motor drives, photovoltaic inverters and digital power supplies, motor control for electric vehicles, and air-conditioning inverters).

The QXS320F280049RevA has a self-developed 32-bit CPU core benchmarked against the TI C28x, providing 150MHz of processing power.

QXS320F280049RevA internal also integrated FPU, TMU and VCU extended instruction set, FPU can provide 32-bit floating-point acceleration instructions, TMU can quickly execute algorithms that contain transformations and torque loop calculations of common trigonometric operations, VCU extended instruction set to reduce the latency of coding applications common complex mathematical operations.

The QXS320F280049RevA utilizes a dual-core architecture, with CPU0 and CPU1 running independently in parallel and communicating with each other. Each core has its own independent storage resources and both have independent access to the major peripherals required in a typical control system. The cores can communicate with each other through interrupts, special registers and shared memory.

The QXS320F280049RevA also integrates high-performance analog peripherals and enhanced control peripherals. Three independent 12-bit conventional ADCs with 3MSPS sampling rates manage multiple analog signals accurately and efficiently, ultimately increasing system throughput. Seven PGAs on the analog front-end enable on-chip voltage regulation prior to conversion. Seven analog comparator modules allow continuous monitoring of input voltage levels for trip conditions. Advanced control peripherals (with frequency-independent ePWM/HRPWM and eCAP) provide excellent control of the system. Built-in 4-channel SDFM allows seamless integration of oversampling Σ-Δ modulators on the isolation layer. Connectivity is supported through a variety of industry-common communication ports (e.g., SPI, SCI, I2C, LIN, and CAN2.0, CAN FD), and multiple multiplexing options are available for excellent signal placement in a wide range of applications. The QXS320F280049RevA supports both PMBus and FSI. Embedded Real-Time Analyzer and Diagnostics (ERAD) modules provide excellent control of the system by The Embedded Real-Time Analysis and Diagnostics (ERAD) module enhances device debugging and system analysis by providing additional hardware breakpoints and counters for analysis.

The QXS320F280049RevA supports up to 256KB of instruction RAM, 256KB of data RAM, and 1MB of Flash memory to accommodate most embedded scenarios.

The QXS320F280049RevA also supports 8KB of bootloader instruction RAM for flexible configuration of the boot process.

| Typology | Caption | Downloading | Dates |

|---|---|---|---|

| Data Sheet | QXS320F280049RevA Digital Signal Controller Datasheet | 2025年05月21日 |

- All

- Hardware Development

- Software Development

- Design Tools

- Seal Inside

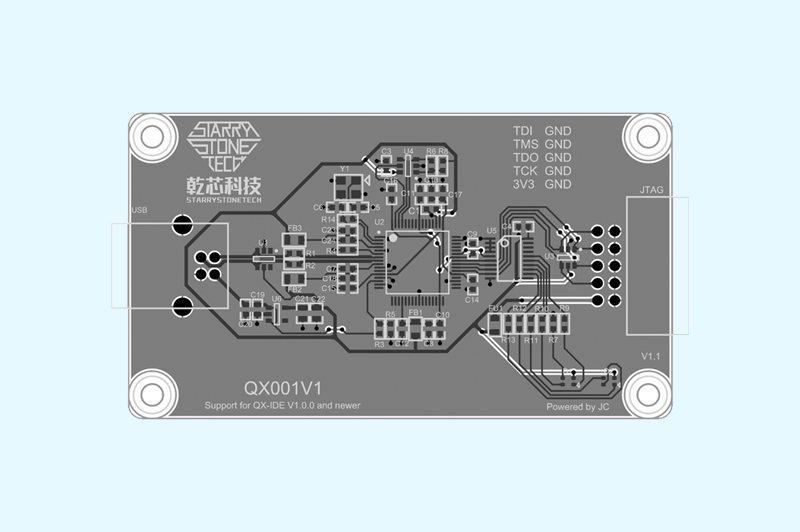

| Typology | Photograph | Caption | Element | Downloading | Dates |

|---|---|---|---|---|---|

| Development Evaluation Boards |  |

QXS320F280049 Development Evaluation Board | QXS320F280049 Development Evaluation Board | 2025年05月28日 |

| Type Code | Typology | Number of pins | Length*Width(mm) | Height/Maximum Height(mm) | Pitch(mm) | Spacing | Package Drawing |

|---|---|---|---|---|---|---|---|

| PZS | LQFP100 | 100 | 14X14 | 1.4/1.6MAX | 0.5 | Not Uploaded | |

| PMS | LQFP64 | 64 | 10X10 | 1.4/1.6MAX | 0.5 | Not Uploaded | |

| RSHS | VQFN56 | 56 | 7X7 | 0.75-0.9/1MAX | 0.4 | Not Uploaded |

| Typology | Photograph | Caption | Element | Downloading | Dates |

|---|---|---|---|---|---|

| Development Evaluation Boards |  |

QXS320F280049 Development Evaluation Board | QXS320F280049 Development Evaluation Board | 2025年05月28日 |

| Type Code | Typology | Number of pins | Length*Width(mm) | Height/Maximum Height(mm) | Pitch(mm) | Spacing | Package Drawing |

|---|---|---|---|---|---|---|---|

| PZS | LQFP100 | 100 | 14X14 | 1.4/1.6MAX | 0.5 | Not Uploaded | |

| PMS | LQFP64 | 64 | 10X10 | 1.4/1.6MAX | 0.5 | Not Uploaded | |

| RSHS | VQFN56 | 56 | 7X7 | 0.75-0.9/1MAX | 0.4 | Not Uploaded |